MOSFETでラッチ回路

作るわけでもないんだが、ON信号が来たらON信号を切ってもOFF信号が来るまでずっとONの回路を考えてみた。

こういうON状態を保持する回路をラッチ回路というらしいんだが、ググってもトランジスタを使う方法しか出てこなくて、MOSFETで作る例が見つからない。

トランジスタで作る回路は、エミッタからベースに流れる電流とコレクタに流れる電流の両方を使って実現するみたいなんだが、なんか両方の電流を使うのは邪道な感じがするし、電流駆動のトランジスタでスイッチを作るって考えが好きじゃない。

というわけで、MOSFETで考えてみた。

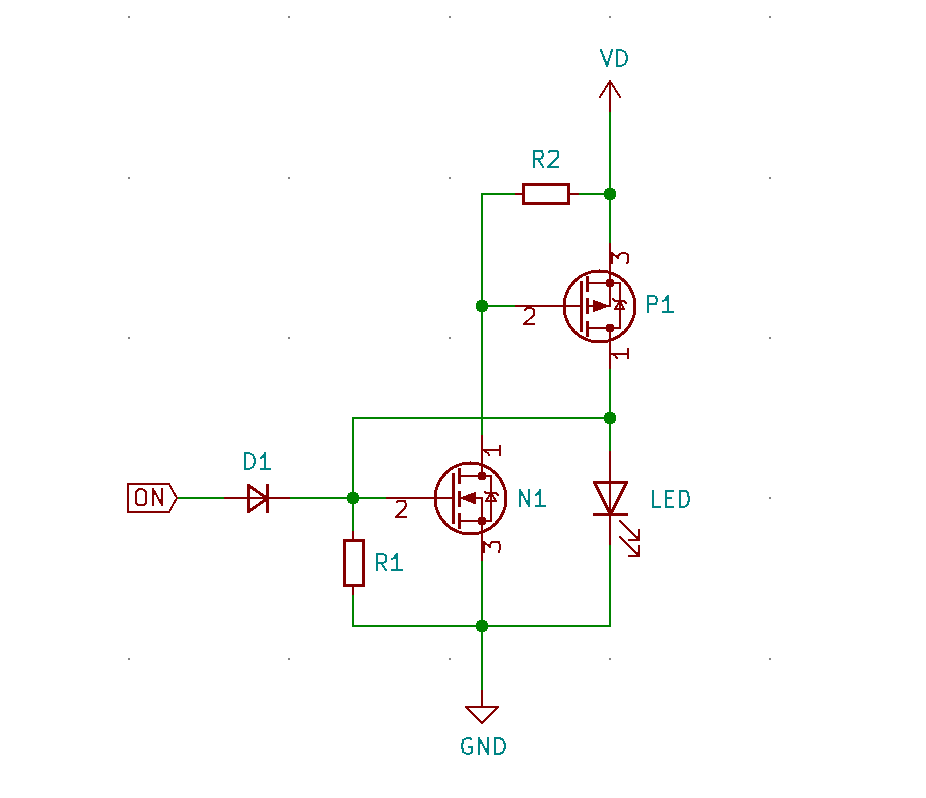

回路1

LEDの部分が動かしたい回路で、P1がPMOSでN1がNMOS。

N1の上の十字の部分はつながってない。交差しないで作る方法はないか?

回路に流れる電流はP1を通ってくるんでP1がOFFならOFFだが、P1のゲートには抵抗を介して電源がつながってる。

P1のゲートからN1を通ってGNDなんで、N1がONならP1のゲートはGNDになるんでN1がONならP1もONになる。

N1のゲートには信号をつなげるんで、信号が来ればN1はONになってP1もONになるので回路は動作する。

P1の下に回路の手前から分岐してN1のゲートにつながってるんで、P1がONならN1もONなんでON状態が保持される。

この際N1のゲート電圧はVDになるんでON信号方向に逆流防止でD1を入れた。なので降下電圧を考えてN1を動かせるだけの信号電圧は必要。

ON状態だとR2を通ってGNDに落ちるんで、ここの部分で電力をロスるね。まあ仕方ないのかな?R1経由もロスるか。

こういうON状態を保持する回路をラッチ回路というらしいんだが、ググってもトランジスタを使う方法しか出てこなくて、MOSFETで作る例が見つからない。

トランジスタで作る回路は、エミッタからベースに流れる電流とコレクタに流れる電流の両方を使って実現するみたいなんだが、なんか両方の電流を使うのは邪道な感じがするし、電流駆動のトランジスタでスイッチを作るって考えが好きじゃない。

というわけで、MOSFETで考えてみた。

回路1

LEDの部分が動かしたい回路で、P1がPMOSでN1がNMOS。

N1の上の十字の部分はつながってない。交差しないで作る方法はないか?

回路に流れる電流はP1を通ってくるんでP1がOFFならOFFだが、P1のゲートには抵抗を介して電源がつながってる。

P1のゲートからN1を通ってGNDなんで、N1がONならP1のゲートはGNDになるんでN1がONならP1もONになる。

N1のゲートには信号をつなげるんで、信号が来ればN1はONになってP1もONになるので回路は動作する。

P1の下に回路の手前から分岐してN1のゲートにつながってるんで、P1がONならN1もONなんでON状態が保持される。

この際N1のゲート電圧はVDになるんでON信号方向に逆流防止でD1を入れた。なので降下電圧を考えてN1を動かせるだけの信号電圧は必要。

ON状態だとR2を通ってGNDに落ちるんで、ここの部分で電力をロスるね。まあ仕方ないのかな?R1経由もロスるか。

でこの状態からOFF信号でOFFにできるようにしなきゃだが、

1の「P1のゲートからGNDに落ちるラインを切る」方法だと、

P1のゲートはON状態だとGNDなんで、ここを分岐してGNDに落とすのは意味がない。

なので、ここを切ろうと思ったら直列にMOSFETを入れるしかないと思うが、ここにNMOSを入れた場合は信号無し状態ならONじゃないとダメなんでNMOSのゲートにはVDをつなぐ必要がある。そうすると切るためにもう1個NMOSが必要になっちゃう。

ここにPMOSを入れた場合は初期状態でONじゃないといけないんでゲートはGNDにつなぐことになる。

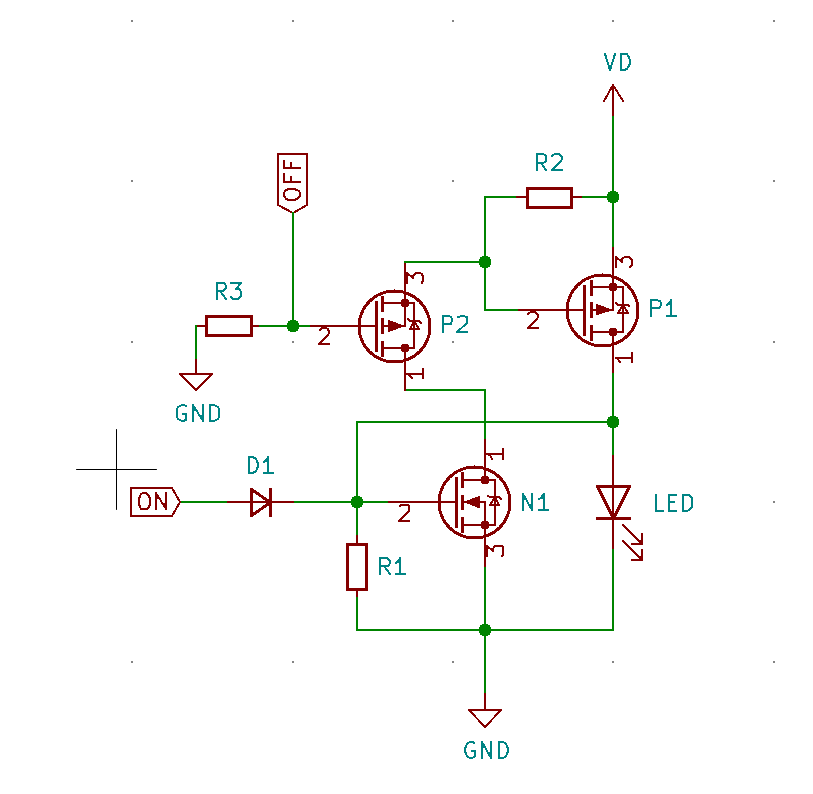

OFF回路1

なんか難しいと思ったんだが、1のルートを遮断する場合これで行ける?

P2のゲートはGNDにつながってるんでOFF信号がなければP2はONなんで元のラッチ回路には影響ないと思う。

ラッチ回路がOFFの場合はN1はOFFなんでP2のソースはVDになる。ラッチ回路がONの場合はN1を通ってGNDなんでP2のソースはGNDになってる。

というわけでOFF信号でP2遮断できる?ちょっと自信ないが・・・

一応、P2が遮断できればP1のゲートがVDになるんでP1がOFFになる。

P2がOFFになったらP2のソースがGNDからVDに変化するからもしかして不安定になるかもしれん?

やっぱMOSFET2個入れたほうがいいのか・・・

2の「P1のドレインからN1のゲートにつながるラインを切る」方法だと、

直列にMOSFETを追加する方法だとソース電圧がGNDより高くするしかないと思うんで信号電圧が高くないと切れなくなるので、やっぱMOSFETを2個入れないとダメな感じがする。

だが、

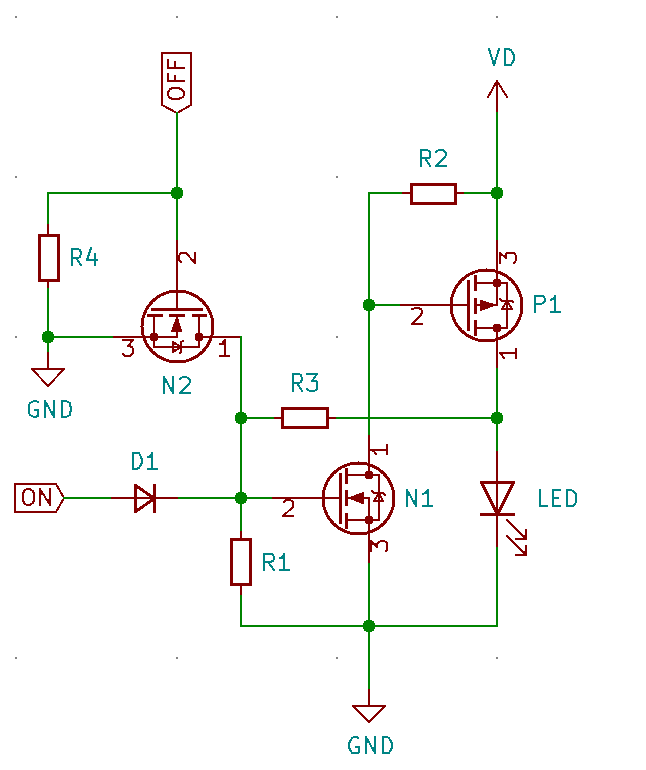

OFF回路2

P1のドレインとN1のゲート間に抵抗(R3)を入れて短絡を防止する必要があるが、

このラインをNMOSを介してGNDに落としてN1を遮断する方法が良さげか?

これならN2のソースはGNDなんでOFF信号で確実にN2をONにできる。

N2がONならN1のゲートはGNDになるんでN1は切れる。

N1が切れれば元のラッチ回路通りP1も切れる。

R3とR1の分圧でN1のゲート電圧は適切に設定する必要はあるがVDの電圧が十分に高いならN1を動かすのに問題なさそうな気はする。

この方法なら問題なさそう。

- P1のゲートからGNDに落ちるラインを切ってP1をOFFにする。

- P1のドレインからN1のゲートにつながるラインを切ってN1をOFFにする。

1の「P1のゲートからGNDに落ちるラインを切る」方法だと、

P1のゲートはON状態だとGNDなんで、ここを分岐してGNDに落とすのは意味がない。

なので、ここを切ろうと思ったら直列にMOSFETを入れるしかないと思うが、ここにNMOSを入れた場合は信号無し状態ならONじゃないとダメなんでNMOSのゲートにはVDをつなぐ必要がある。そうすると切るためにもう1個NMOSが必要になっちゃう。

ここにPMOSを入れた場合は初期状態でONじゃないといけないんでゲートはGNDにつなぐことになる。

OFF回路1

なんか難しいと思ったんだが、1のルートを遮断する場合これで行ける?

P2のゲートはGNDにつながってるんでOFF信号がなければP2はONなんで元のラッチ回路には影響ないと思う。

ラッチ回路がOFFの場合はN1はOFFなんでP2のソースはVDになる。ラッチ回路がONの場合はN1を通ってGNDなんでP2のソースはGNDになってる。

というわけでOFF信号でP2遮断できる?ちょっと自信ないが・・・

一応、P2が遮断できればP1のゲートがVDになるんでP1がOFFになる。

P2がOFFになったらP2のソースがGNDからVDに変化するからもしかして不安定になるかもしれん?

やっぱMOSFET2個入れたほうがいいのか・・・

2の「P1のドレインからN1のゲートにつながるラインを切る」方法だと、

直列にMOSFETを追加する方法だとソース電圧がGNDより高くするしかないと思うんで信号電圧が高くないと切れなくなるので、やっぱMOSFETを2個入れないとダメな感じがする。

だが、

OFF回路2

P1のドレインとN1のゲート間に抵抗(R3)を入れて短絡を防止する必要があるが、

このラインをNMOSを介してGNDに落としてN1を遮断する方法が良さげか?

これならN2のソースはGNDなんでOFF信号で確実にN2をONにできる。

N2がONならN1のゲートはGNDになるんでN1は切れる。

N1が切れれば元のラッチ回路通りP1も切れる。

R3とR1の分圧でN1のゲート電圧は適切に設定する必要はあるがVDの電圧が十分に高いならN1を動かすのに問題なさそうな気はする。

この方法なら問題なさそう。